#### Open Source Digital Logic Design Using open source tools for designing, testing, and synthesising Verilog modules

Davis Claiborne

LUG @ NC State

August 31, 2021

# **Linux Users Group** at NC State University

Boolean algebra Finite State Machines Optimization

## What is digital logic?

- Circuits need to do things

- Claude Shannon: A Symbolic Analysis of Relay and Switching Circuits

- Representing circuits with Boolean algebra

- Boolean: 0 or 1 (high/low voltage)

[11]

- Basically, digital logic is getting circuits to do things

- For a long time, getting circuits to do thing thing you wanted was more of an art than a science

- That was true until Claude Shannon proved that any circuit can be represented using Boolean algebra; previous study showed that any logic expression can be expressed with Boolean algebra

Boolean algebra Finite State Machines

# What is Boolean algebra?

- Values can be 0/1, F/T, etc.

- Basic operations are "and," "or," and "not"

- These are required to represent any expression

- More operators exist<sup>1</sup>

- Can only answer yes or no questions

- If you abstract the yes or no questions enough, can do math-more later

And for some, a single one (e.g. NAND) can represent all logic operations! Open Source Digital Logic Design Davis Claiborne

- So what exactly is Boolean algebra?

- Basically, Boolean algebra is using two opposite states, usually represented as 0 and 1, true and false, or some other pair to represent logic expressions

- Using the basic operators and, or, and not, any logic expression can be represented

- Now, you may be wondering: what can Boolean algebra answer? What exactly is a logic expression?

- Boolean algebra can answer any question that can be answered strictly with "yes" or "no" questions

- Those of you more in the know know that last statement isn't totally true - I'll get back to that later, don't worry

Boolean algebra Finite State Machines

## Notation

|     | Logic notation   | EE expression               | Logic gates                                             |

|-----|------------------|-----------------------------|---------------------------------------------------------|

| And | $Z = X \wedge Y$ | $Z = X \cdot Y$             | $\begin{array}{c} X \\ Y \end{array} \longrightarrow Z$ |

| Or  | $Z = X \lor Y$   | Z = X + Y                   | $X \longrightarrow Z$                                   |

| Not | $\neg X$         | $\overline{X}$ <sup>1</sup> | $X \longrightarrow \overline{X}$                        |

<sup>1</sup> Sometimes you'll see people use a single apostrophe/tick as well, i.e.  $X^\prime$ Open Source Digital Logic Design

```

Open Source Digital Logic Design

```

- There are three primary notations: formal logic notation, the electrical engineering expression form, and logic gate notation, which is also used by electrical engineers

- As a somewhat biased electrical/computer engineer, I much prefer the last two, just because those are what I'm used to seeing

- If you're wondering why ECE people use two representations, the reason is essentially just that the two different notations are good for different things; the expressions are much more compact and easier to optimize (generally), but logic gates are much easier to look at and follow visually

Boolean algebra Finite State Machines Optimization

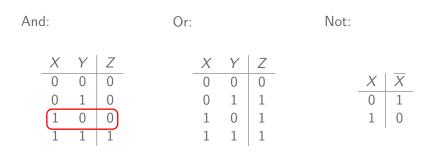

## Truth tables

```

Open Source Digital Logic Design

```

| Truth tables                                          |                         |      |

|-------------------------------------------------------|-------------------------|------|

| And:                                                  | Or:                     | Not: |

| X Y Z                                                 | X Y Z                   | . ×I |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | 0 1 1<br>1 0 1<br>1 1 1 | 0    |

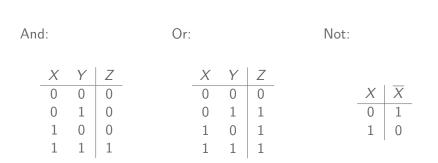

- Truth tables are one way of analyzing the outputs of logical expressions

- They show the output for every permutation of inputs; the order of the inputs is traditionally done starting at all zeros and going to all 1s, alternating bits starting from the right until all permutations are seen

- Here I'm showing the truth tables for the 3 basic logic gates

- Reading them isn't too hard, just think of it as a true or false problem

Boolean algebra Finite State Machines Optimization

## Truth tables

Is X true AND is Y true? No

For instance, here's a quick example: in the highlighted row of this truth table, are X and Y both true? The answer is no, since Y is 0 (false)

Boolean algebra Finite State Machines Optimization

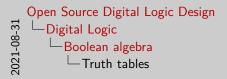

## Truth tables

Is X true AND is Y true? Yes

```

Open Source Digital Logic Design

```

- Here's another quick example: are X and Y both true now? The answer is yes, because both X and Y are 1

- So, why do we use truth tables?

- Basically, they're just another way to help look at how the inputs and outputs relate for a given input

Boolean algebra Finite State Machines Optimization

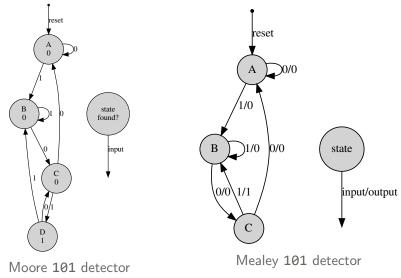

## Finite State Machines

• Allow more complex, useful circuits

- Two main types:

- Moore: Output depends only on state

- Mealey: Output depends on state and inputs

• How to store state?

- Finite state machines are a way to make more complex, useful circuits by adding state information to them

- They're really more of a design tool, since all these things could be done without a state machine, it would just be a pain

- There are two main types, Moore and Mealey

- The main difference between the two is whether the output depends on the input or not: for Moore it depends only on the state, for Mealey it also depends on te inputs

- What this means is that Moore machines tend to be larger and simpler, while Mealey machines are smaller, but more complex

Boolean algebra Finite State Machines Optimization

## Moore vs Mealey

Davis Claiborne

- Here are two example FSMs where you can see the differences between More and Mealey more easily

- Both are looking to detect the input pattern "101", but look fairly different

- Let's start looking at the Moore FSM:

- To the rigt of the graph you can see the general template of how to read this graph: each circle is a state, where the top line shows the name and the bottom line shows the output; arrows coming out of the circle represent an input causing the state to change

- Starting at A, since that where it gets reset to, it should be fairly easy to convince yourself this does, in fact, work

- Now, let's look at the Mealey FSM:

- In its case, the circle just represents a state, since Mealey FSM outputs relay in the state and the input, which is why the output is part of the arrow here

- One thing I've kind of glossed over so far, is how do you store information in digital logic? Not just in FSMs, but in general?

Boolean algebra Finite State Machines Optimization

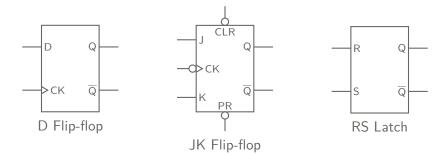

# Storage

• Flip-flops, latches, registers

- Triangle often represents clock

- Circle represents active low logic

- Storage in circuits is done using what are known as flip-flops, latches, or registers

- The terminology you use depends on a lot of different things, but for the most part the terms are interchangeable enough at *a high level* that it doesn't really matter

- In reality, these elements all differ in their implementation and use, but I won't go too deep into them here

- I will point out a few general things for reading these, though:

- Note how the D and JK FF have an input called CK that stands for "clock," and is often represented with the triangle on the pin

- The circle you see on some of the pins on the JK FF means that it uses "active low" logic

Boolean algebra Finite State Machines Optimization

# Why optimize?

- Fewer components

- Cheaper

- Simpler

- Faster

- Efficient

• So how is it done?

```

Open Source Digital Logic Design

```

| w | Why optimize?                        |  |  |  |  |

|---|--------------------------------------|--|--|--|--|

|   |                                      |  |  |  |  |

|   | <ul> <li>Fewer components</li> </ul> |  |  |  |  |

|   | Cheaper                              |  |  |  |  |

|   | Simpler                              |  |  |  |  |

|   | • Faster                             |  |  |  |  |

|   | Efficient                            |  |  |  |  |

|   |                                      |  |  |  |  |

|   | · So how is it done?                 |  |  |  |  |

|   |                                      |  |  |  |  |

- One of the key benefits Claude Shannon brought to digital logic with the introduction of Boolean algebra was a reliable way to optimize the expressions down to simpler formats

- Optimized expressions offer a number of advantages; by reducing the number of components in a circuit, you can make it cheaper, simpler, faster, and more efficient

- Optimize circuits are less expensive because they have fewer components

- They're easier to debug because they're simpler, making it faster to find mistakes

- They're faster, because each component introduces propogation delay as the current travels through it

- They're more efficient because each component consumes power

- There are a number of tecniques for performing optimization that I'll quickly discuss

Finite State Machines Optimization

### Optimization technique 1: Reduce logic expressions

- Theorems:

- X + 0 = X• X + X = X

- X + 1 = 1

- $X \cdot 0 = 0$

- $X \cdot 1 = X$ •  $(\overline{X}) = X$

- $X + \overline{X} = 1$

- $X \cdot X = X$

- $X \cdot \overline{X} = 0$

- X(Y+Z) = XY + XZ

- XY + X7 = X7 + XY

- These can be used to help reduce expressions:

•

$$XY + \overline{X}Y = Y(X + \overline{X}) = Y \cdot 1 = Y$$

- In Boolean algebra, there are a number of theorems that can be used to reduce logic expressions

- Here are some of the more simple theorems I won't go through them all or prove them for the sake of brevity, but most of them can be proven fairly easily just by drawing the truth table

- You can reduce logic expressions using these theorems (in both directions) to eliminate redundant terms

- The main problem with this technique is that it requires a bit of practice for some of the longer, more complicated expressions, and it just isn't really all that efficient to do - lots of guess and check

Boolean algebra Finite State Machines Optimization

## More theorems: De Morgan's Law

•

$$\overline{(A+B)} = \overline{A} \cdot \overline{B}$$

•

$$\overline{(A \cdot B)} = \overline{A} + \overline{B}$$

• "Break the line, change the sign"

[12]

$$\overline{(\overline{A} + \overline{B} + \overline{C})(\overline{A} + \overline{B} + C)} = \overline{\overline{A} + \overline{B} + \overline{C}} + \overline{\overline{A} + \overline{B} + C} = \overline{\overline{A}} = \overline{\overline{B}} = \overline{\overline{C}} + \overline{\overline{A}} = \overline{\overline{B}} = \overline{\overline{C}} = \overline{\overline{A}} = \overline{\overline{A}} = \overline{\overline{C}} = \overline{\overline{A}} = \overline{\overline{A}} = \overline{\overline{C}} = \overline{\overline{A}} = \overline{\overline{C}} = \overline{\overline{A}} = \overline{\overline{A}} = \overline{\overline{C}} = \overline{\overline{A}} = \overline{\overline{A}$$

- One of the more advanced theorems I'll cover here is called De Morgan's Law, which lets you distribute inversion operations

- In my opinion, it's easier to visualize using set theory, which you can see on the right

- In the first part of the picture, you can read it as "everything that's not in A or B is the same as everything that's not in A combined with everything not in B"

- Similarly, in the bottom picture, you can read it as "everything not in the intersection of A and B is the same as everything not in A combined with everything not in B"

- A way to remember how to do it: "Break the line, change the sign"

- Here's a good example of why this is so useful: you *could* FOIL out those terms, find all the like terms, etc., but De Morgan's is so much easier and faster to do

Boolean algebra Finite State Machines Optimization

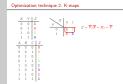

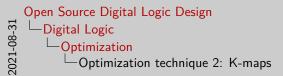

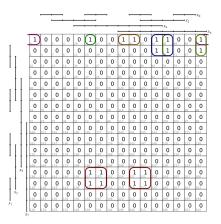

## Optimization technique 2: K-maps

Davis Claiborne

- Karnaugh maps, usually called K-maps, are another tool that you can use to help reduce logic expressions

- The basic concept is to rearrange the truth table such that *only one of the inputs changes* as you change columns or rows, *even when you wrap around*

- That's a little jargony, so it's easier to look at an example; let's put the first truth table into a k-map

Boolean algebra Finite State Machines Optimization

1 1 0

## Optimization technique 2: K-maps

|   | X | Y | Z | 7 |   |   | <i>, ,</i> | $\langle  $ | 0 |

|---|---|---|---|---|---|---|------------|-------------|---|

|   | 0 | 0 | 1 |   |   | ) | $\sim$     |             | 0 |

|   | 0 | 1 | 0 |   |   |   | 0          |             | 1 |

|   | 1 | 0 | 1 |   |   |   | 1          |             | 0 |

|   | 1 | 1 | 0 |   |   |   |            | I           |   |

|   | A | В | С | Ζ |   |   |            |             |   |

| _ | 0 | 0 | 0 | 0 | _ |   |            |             |   |

|   | 0 | 0 | 1 | 0 |   |   |            |             |   |

|   | 0 | 1 | 0 | 1 |   |   |            |             |   |

|   | 0 | 1 | 1 | 1 |   |   |            |             |   |

|   | 1 | 0 | 0 | 1 |   |   |            |             |   |

|   | 1 | 0 | 1 | 0 |   |   |            |             |   |

|   | 1 | 1 | 0 | 1 |   |   |            |             |   |

|   | 1 | 1 | 1 | 1 |   |   |            |             |   |

- I've color coded the items to help show the transformation

- Reading these is a lot like consulting a table; for a given row or column, the specified value of X applies

- Now that the items are in the table, you can circle groups of contiguous 1s that are a power of two size and rectangular, maximizing the size of each grouping

Boolean algebra Finite State Machines Optimization

## Optimization technique 2: K-maps

| 0<br>0<br>1  | Y     Z       0     1       1     0       0     1       1     0 |   | $ \begin{array}{c cccc} X & 0 & 1 \\ \hline 0 & 1 & 1 \\ 1 & 0 & 0 \end{array} $ | $Z = \overline{Y}(\overline{X} + X) = \overline{Y}$ |

|--------------|-----------------------------------------------------------------|---|----------------------------------------------------------------------------------|-----------------------------------------------------|

| A B          | С                                                               | Ζ |                                                                                  |                                                     |

| 0 0          | 0                                                               | 0 |                                                                                  |                                                     |

| 0 0          | 1                                                               | 0 |                                                                                  |                                                     |

| 0 1          | 0                                                               | 1 |                                                                                  |                                                     |

| 0 1          | 1                                                               | 1 |                                                                                  |                                                     |

| 1 0          | 0                                                               | 1 |                                                                                  |                                                     |

| 1 0          | 1                                                               | 0 |                                                                                  |                                                     |

| 1 1          | 0                                                               | 1 |                                                                                  |                                                     |

| 1 1          | 1                                                               | 1 |                                                                                  |                                                     |

| Davis Claibo | rne                                                             |   | Open Source Digital Logic D                                                      | esign 11                                            |

- For instance, here the first row has 2 1s in a rectangle; since 2 is a power of 2, you can group them

- Each grouping corresponds to a part of the final expression

- You can find that expression by looking at the columns and rows shared and doing some optimizations

- This may seem like optimization 1 with extra steps, but the main advantage of this is that it's fast, reliable, and easy to do

- The reason this works is precisely *because* of the way the table was layed out - by only changing one term at a time, it makes logic simplifications always reduce (when done properly)

Boolean algebra Finite State Machines Optimization

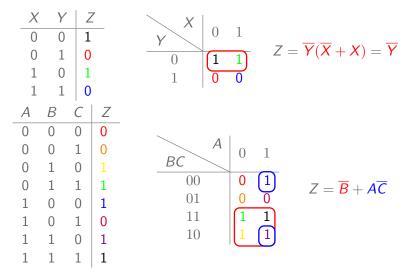

#### Optimization technique 2: K-maps

Davis Claiborne

- Now let's look at a more complicated case. This one's a bit tricker to set up - notice how in the third row it goes from 01 to 11 in this is so that only one term changes at once

- After filling in the table, we can do the same process as before: find rectangular power of 2-size groups of 1

- And remember: you can wrap "around" the top and bottom or left and right of the table, since it's still only one term that's changing, and you always want to go for the largest groupings possible

Boolean algebra Finite State Machines Optimization

#### Optimization technique 2: K-maps

Davis Claiborne

- Here's the final result for that grouping

- There's a few things to notice here:

- First, notice how the blue grouping wrapped around the top and bottom, becoming term A C'

- As an aside, this is part of the reason why I think it's actually easier to think of this as a sphere, though that's harder to show

- Next, notice how larger groups are preferred: the red block could have been two distinct blocks of 2 each, but since it would simplify out anyways, it's easier to have a single block

- Finally, notice how ABC' is in two groups, B' and AC'. At first, covering it twice might seem like a waste. But counting it twice actually allows us to simplify: instead of AB'C' we can have just AC'.

Boolean algebra Finite State Machines Optimization

3D K-maps: AKA when did this become topography?

4 variables:

| • 0000              | 0100 | 1100 | 1000 • |

|---------------------|------|------|--------|

| 0001                | 0101 | 1101 | 1001   |

| 0011                | 0111 | 1111 | 1011   |

| <mark>_</mark> 0010 | 0110 | 1110 | 1010   |

#### Open Source Digital Logic Design Digital Logic Optimization -3D K-maps: AKA when did this become topography?

- Beyond 4 variables in a K-map, you have to do some fiddling around to get the topopgrahy to cooperate properly

- One of the simplest ways to do this is to overlay two matrices on top of each other

- If these maps get too much larger, you run into an issue, as you either won't get the most efficient possible expression anymore or you'll get an incorrect expression depending on how the terms are laid out

- This is another reason I prefer thinking of K-maps as curved shapes shapes like cylinders, spheres, and toruses, as they implicitly remind you of the limitations of these representations

- Excuse the mostly horrible images drawn by me... these things are well beyond my tikz-fu

Boolean algebra Finite State Machines Optimization

# Beyond six variables: Try not to

8 variables<sup>1</sup>:

y=(ຄັງຄັນຄຸ້ນຄູ່ນັ້ງຄັນ) v (ຄັງຊັນຊານອຸດັນອຸດັນອຸດັນ) v (ຄາຊອົງຊັນຊົນ) v (ຄາຊອົງຊັນຊົນ) v (ຄາອັງຊາດອາດ)

[10]

<sup>1</sup> Technically, this is a Karnaugh-Veitch chart, but whatever

Davis Claiborne

#### Open Source Digital Logic Design

13 / 28

- There is a limit to how useful a K-map can become; after a certain point, it becomes more academic than practical in my opinion

- All the mirroring, odd group sizes, etc., make this pretty tedious to do

- This about wraps up all that I really feel I need to cover for digital logic for now - there's a lot more that I *could* cover, but you're not prepping for the FE exam or anything, so I'll leave it here for now

- In case you're curious about how expressions with more than six variables are optimized...

- There are other tools to aid performing this process by hand, like Reduced Karnaugh maps, but it's mostly reserved for computers, who are much better at doing tedious things, both in terms of speed and error rate

Overview Syntax Testing

# Specifying the circuit

• Need to specify logic circuit to computer

• "Compiling" (+synthesis) optimizes logic

- Hardware description languages:

- Verilog

- VHDL (VHSIC (Very High Speed Integrated Circuit) HDL)

#### Specifying the circuit

- · Need to specify logic circuit to compute

- "Compiling" (+synthesis) optimizes logic

- Hardware description languages:

Venlog

VHDL (VHSIC (Very High Speed Integrated Circuit) HDL)

- The first step into getting computers to do the optimization work for you is... telling the computer what your circuit is

- Parts of this process can be considered fairly similar to what a compiler is doing as it optimizes your code; this is usually done during the synthesis step

- There are a few major ways to specify your circuit, the most common being what are called "Hardware description languages," or HDLs, like Verilog and VHDL

- For this presentation, I'll talk about Verilog, just because I know the most about it, though both HDLs see wide use

Overview Syntax Testing

What is Verilog?

• HDL with C-like syntax

- Two parts of language:

- Synthesizable: Can be represented as circuit

- Unsynthesizable: Exists for logic verification

• Non-linear execution

```

Open Source Digital Logic Design

Understand

Understand</t

```

| What | is Verilog?                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------|

|      | HDL with C-like syntax                                                                                                     |

|      | Two parts of language:<br>• Synthesizable: Can be represented as circui<br>• Unsynthesizable: Exists for logic verificatio |

|      | Non-linear execution                                                                                                       |

- Verilog is a hardware description language designed with a C-like syntax

- Verilog can be broken down into two key parts: synthesizable and unsynthesizable

- The synthesizable portion of Verilog is what's used to optimize the logic expressions mentioned earlier

- The unsynthesizable part is used to help test your circuits to ensure they're doing what you want

- One important thing to keep in mind when working with Verilog is that it's **not** a traditional programming language, because it does not run linearly

- This can be hard to wrap your head around at first, but it's important to remember this, because the code is describing a circuit, which (of course) does not run linearly

Digital Logic Overview Verilog Syntax Software Testing

### Basic syntax

Terminology:

- Module: logic circuit; functions

- Port: inputs/outputs to module; parameters

```

module and behavioral(

input wire a, b, // Input ports

output reg z // Output ports

);

// always @(): Reevaluate any time a or b changes

// Think of this like a while-true that only executes when its inputs change

always @( a or b ) begin

// 1'b1: one bit long number binary 1

// &&: logical and

// begin: {; end: }

if ( a == 1'b1 && b == 1'b1 ) begin

z = 1'b1;

end

else begin

z = 1'b0;

end

end

endmodule

```

- In Verilog, any time someone says "module," you can think of it as if it were a function in a normal

programming language

- Any time someone says "port," they mean the inputs and outputs of a module, which can be thought of as the parameters to a function

- Now, let's start looking at the code itself

- This code creates a module called "and\_behavioral," which has two inputs, a and b, and an output, z

- Notice that the output is a reg: confusingly, this is different from the register memory storage elements

- Right off the bat, I'm throwing a kind of tricky piece of syntax at you: "always @" statements are used to

constantly reevaluated every time one of the inputs changes

- · You can think of this like an infinite loop that only runs if one of its inputs has changed

- Inside this block, we have an if-else statement

- To read the conditional, it's important to know that 1'b1 is just Verilog's way of saying "a one-bit value of binary 1"

- One unusual part of Verilog's syntax is that it eschews the use of curly braces for "begin" and "end" instead

- · If you're wondering about the difference between a wire or a reg, don't worry I'll get to it

Back systax Tenning: • Andre legis Christ, barten • Start, specification to model, parameters • Start, specification to model, parameters • Start, specification to model and start • Start, specifica Digital Logic Overvie Verilog Syntax Software Testing

### Different styles of Verilog

**Gate-level**: Define circuit by basic logic gates; uses gate primitives **Dataflow**: Define circuit by function; uses built-in operators **Behavioral**: Define circuit by output; uses if/else/switch/etc.

```

// Port types in-module

module and gatelevel( a, b, z );

input wire a, b;

// Port types as parameters

output wire z;

module and behavioral(

input wire a, b,

// Gate-level

output reg z

// Name of and gate is `u1`

);

AND u1 ( z, a, b );

// Behavioral

endmodule

always @( a or b ) begin

if ( a == 1'b1 && b == 1'b1 ) begin

// Port types as parameters

z = 1'b1;

module and dataflow(

end

input wire a, b,

else begin

output wire z

z = 1'b0;

end

end

// Dataflow

assign z = a \& b;

endmodule

endmodule

```

- Difficult system of verticity. Catabase index constraints have been been approximately approximatel

- Now that we have a basic understanding of Verilog's syntax, lets look at some of the different styles you

can use

- · First, take a look at and\_gatelevel, which shows the gate-level style of Verilog

- This is the most intuitive for us EEs, since it breaks down the circuit into basic logic-gates

- Also note that this module is using in-module annotations; both versions are acceptable, but I prefer annotating the ports as parameters because I find it less prone to mistakes

- Up next is and\_dataflow, which demonstrates the dataflow style of Verilog.

- Dataflow can be considered a step-above gate-level in terms of abstraction; by using the built-in operators you can abstract away thinking about low-level gates and instead focus on what the module is doing

- Finally, there's behavioral, the highest abstraction-level. I showed this first because it's the easiest for

programmers to think of; by defining the module just in terms of inputs and outputs, you can abstract

away virtually all parts of the circuit itself

- You may be asking yourself, "why bother with gate-level or dataflow when behavioral just does it all for you?" And that's a very fair question. Gate-level and dataflow are used today mostly for verification, since synthesis tools create efficient enough chips for the vast majority of cases

- = Essentially, it can be considered writing C/Java/etc. vs assembly

Digital Logic Overview Verilog Syntax Software Testing

#### Testing Verilog: Test benches

```

module and tb; // tb = test bench

reg a, b, // AND inputs

check; // Bit toggled to trigger check

wire z dataflow, z behavioral; // Outputs

// Creates modules to test

// .<x>(<v>) specifies that <v> should be assigned to port <x>

// Typically, module being tested is called DUT

and dataflow add1( .a( a ), .b( b ), .z( z dataflow ) );

and behavioral add2(.a(a), .b(b), .z(z behavioral));

// Shows outputs for manual checking

// More sophisticated checking methods exist

always @( check ) begin

$display(

"Time: %d a: %b b: %b z df: %b z bh: %b",

$time, a, b, z dataflow, z behavioral

);

end

// Changes values

initial begin

// #<x> = Go forward <x> clock cycles; ~ = toggle bits

#1 a = 0; b = 0; check = 0; // Time: 1 a: 0 b: 0 z df: 0 z bh: 0

#1 a = 0; b = 1; check = ~check; // Time: 2 a: 0 b: 1 z df: 0 z bh: 0

#1 a = 1; b = 0; check = ~check; // Time: 3 a: 1 b: 0 z df: 0 z bh: 0

#1 a = 1: b = 1: check = ~check: // Time: 4 a: 1 b: 1 z df: 1 z bh: 1

end

endmodule

```

```

Open Source Digital Logic Design

```

- Now that we've written our Verilog module, we need a way to ensure that we've written it correctly

- Verilog does this using what's known as a test-bench

- Here you can see the basic layout of a testbench it's actually very similar to a module

- That's because it is a module, just without any ports/IO

- Here we create 3 regs: a and b, to hold the inputs to the adders, and check, which we'll use to trigger the output function

- We also create two wires, one for each of the outputs

- Next, the two modules are instantiated, add1 and add2, which are the dataflow and behavioral versions of the modules we created earlier

- Traditionally, the module being tested will be given the name DUT, but since two modules are being tested here, I can't do that

- Next, the always@ statement triggers output showing the current state of the circuit when check changes

- Finally, we have the code responsible for changing the values

Digital Logic Overvie Verilog Syntax Software Testing

#### Automated test benches

module and\_tb\_selfchecking;

```

reg [1:0] inputs [3:0]; // 4 inputs, 2 bits each

reg outputs [3:0]; // 4 outputs, 1 bit each

reg a, b, clk, reset; // clk and reset are to prevent sim issues

wire z dataflow, z behavioral;

integer i, errors; // index for inputs/outputs, # errors

// Creates modules to test

and dataflow add2( .a( a ), .b( b ), .z( z dataflow ) );

and behavioral add3( .a( a ), .b( b ), .z( z behavioral ) );

// Pulses clock

always begin #5; clk = ~clk; end

// Initializes values

initial begin

inputs[0] = 2'b00; inputs[1] = 2'b01; inputs[2] = 2'b10; inputs[3] = 2'b11;

outputs[0] = 1'b0; outputs[1] = 1'b0; outputs[2] = 1'b0; outputs[3] = 1'b1;

errors = 0; i = 0; clk = 0;

reset = 1; #1 reset = 0;

end

// Assigns inputs; posedge means to only do it on the rising edge

// (only when it changes from 0 to 1)

always @( posedge clk ) begin

#1 { a, b } = inputs[i]; // 'Unpacks' inputs[i] into a and b

end

// Continued

```

- There is a way to automate test benches so that you don't need to manually check if your outputs are right

- However, it's much more complex, and very prone to simulation issues caused by the non-sequential code operation

- Basically, some values in Verilog will change before others in an indeterminate manner, so you need to carefully design your tests around this fact

- I won't spend a ton of time going over how this is constructed, since it's a bit complicated, but I just figured I'd mention that it is possible to do

Digital Logic Overview Verilog Syntax Software Testing

#### Automated test benches (cont)

```

always @( negedge clk ) begin

if ( ~reset ) begin

// !==: Special kind of compare; doesn't ignore X's (don't cares)

if ( z dataflow !== outputs[i] ) begin

$display(

"dataflow %d failed: %d vs %d",

i, z dataflow, outputs[i]

errors = errors + 1;

end

if ( z behavioral !== outputs[i] ) begin

$display(

"behavioral %d failed: %d vs %d",

i, z behavioral, outputs[i]

);

errors = errors + 1;

end

// Unless we have a test input of don't cares (which would be

// pretty unusual), this is a fine way to see if we're at the end

i = i + 1;

if ( inputs[i] === 2'bx ) begin

$display( "Test completed with %d errors", errors );

$finish:

end

end

end

endmodule

```

Davis Claiborne

- More of the automated testing. I can go over this more at the end if people are interested and there's time

- A lot of the differences have to do with HDLs vs programming languages, and how you don't have control over when certain expressions are evaluated

- There's a lot of Verilog I haven't even covered, like blocking vs non-blocking, registers vs wires, and the finer points of Verilog's number representation and expansion, but I think this is enough for now

Simulation/Debugging Synthesis

# Simulating Verilog—Option 1: Icarus

Website [6]

Basic usage:

- \$ iverilog -o out -s top file.v

- -o: Output executable; run this to simulate

- -s: Top-level module to simulate (or all if excluded)

- \$ vvp out

- Performs simulation

Davis Claiborne

- Now that we've written all this Verilog code, it's time to actually simulate it

- Tons of simulators exist, but most of them are closed-source, or proprietary

- One that isn't, however, is called "Icarus Verilog"

- I won't go over installing it here, but I will give a quick overview of how to use it

- (See slide)

- There's a few more parts to this that I'll talk about later, but this is the gist of it

Simulation/Debugging Synthesis

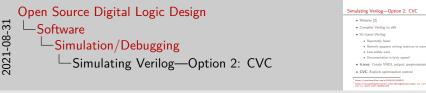

# Simulating Verilog—Option 2: CVC

- Website [2]

- Compiles Verilog to x86

- Vs Icarus Verilog:

- Reportedly faster

- Natively supports writing matrices to wave files<sup>1</sup>

- Less-widely used

- Documentation is fairly sparse<sup>2</sup>

- Icarus: Create VHDL output; preprocessors

- CVC: Explicit optimization control

https://stackoverflow.com/a/22395232/2238176

<sup>//</sup>raw.githubusercontent.com/cambridgehackers/open-src-cvc/master/doc/ oss-cvc-quick-start-061014.pdf

- Another option for simulating Verilog is CVC

- CVC compiles your verilog to x86 instructions to simulate, which reportedly improves speed, though I didn't bother checking this myself

- Another advantage of CVC over lcarus is that it can write matrix variables to wavefiles without having to do a workaround

- There are some downsides, however:

- CVC is less-widely used than Icarus, making support for it harder to find

- Documentation in general is pretty sparse: their website itself doesn't even have the documentation; it apparently comes with the code, but can also be found mirrored on GitHub

- Finally, each simulator has some different options

- Icarus can convert your Verilog to VHDL, and can also extend Verilog's functionality by adding preprocessor

- While Icarus does optimization, CVC gives you more explicit control of which optimizations to do

Simulation/Debugging Synthesis

## GTKWave

Waveform viewer

Export wavefiles:

```

initial begin

$dumpfile( "waves.vcd" );

$dumpvars; // write all vars

end

```

More efficient wavefiles:

\$ vvp out -fst

CVC-specific:

```

initial begin

$fstDumpfile( "waves.fst" );

$fstDumpvars; // write all vars

end

```

#### GTKWave's incredible logo

An experienced professional shown violating most known rules of electrical safety with GTKWave. Please do not attempt this at home.

[6]

\$ cvc +dump\_arrays and.v

Davis Claiborne

Open Source Digital Logic Design

- GTKWave is a free, open-source waveform viewer with one of the best logos I've ever seen

- In case you don't know what a waveform viewer is, it's basically just a graphical way to view the relationship between signals

- Verilog has builtin commands for exporting wave files: \$dumpfile specifies the file to write to, and \$dumpvars specifies which variables to write (writes all by default)

- Additionally, most simulators offer support for more efficient wavefiles

- For instance, with lcarus, using vvp with the -fst flag to specify that wavefiles should be fsts

- For CVC, you need to explicitly use their fst-specific commands; the dump\_arrays option includes arrays in wavefiles

Simulation/Debugging Synthesis

### GTKWave in action

| -SST<br>→and_tb<br>→and_tb_selfchecking<br>→and1<br>→and2 |                | Signals                     | Waves   | ା Marker: +5 ns   Cursor: 20 ns<br>Waves |       |       |       |       |       |       |      |   |  |

|-----------------------------------------------------------|----------------|-----------------------------|---------|------------------------------------------|-------|-------|-------|-------|-------|-------|------|---|--|

|                                                           |                |                             | ns 8 ns | 8 ns                                     | 12 ns | 16 ns | 20 ns | 24 ns | 28 ns | 32 ns | 36 n | 4 |  |

|                                                           |                | z=<br>testbench             |         |                                          |       |       |       |       |       |       |      |   |  |

| ype                                                       | Signals        | a=                          |         |                                          |       |       |       |       |       |       |      |   |  |

| ntege                                                     | r errors       | b=                          |         |                                          |       |       |       |       |       |       |      |   |  |

| ntege                                                     | ri             | clk=                        |         |                                          |       |       |       |       |       |       |      |   |  |

| eg                                                        | inputs[0][1:0] | errors=                     |         |                                          |       |       |       |       |       |       |      |   |  |

| eq                                                        | inputs[1][1:0] | i=<br>inputs[0][1:0]=       |         |                                          |       |       |       |       |       |       |      |   |  |

| eq                                                        | inputs[2][1:0] | inputs[1][1:0]=             |         |                                          |       |       |       |       |       |       |      |   |  |

| ea                                                        | inputs[3][1:0] | inputs[2][1:0]=             |         |                                          |       |       |       |       |       |       |      |   |  |

| -                                                         |                | inputs[3][1:0]=             |         |                                          |       |       |       |       |       |       |      |   |  |

| eg                                                        | outputs[0][0]  | outputs[0][0]=              |         |                                          |       |       |       |       |       |       |      |   |  |

| eg                                                        | outputs[1][0]  | outputs[1][0]=              |         |                                          |       |       |       |       |       |       |      |   |  |

| eg                                                        | outputs[2][0]  | outputs[2][0]=              |         |                                          |       |       |       |       |       |       |      |   |  |

| eg                                                        | outputs[3][0]  | outputs[3][0]=              |         |                                          |       |       |       |       |       |       |      |   |  |

| pe                                                        | reset          | reset=<br>z behavioral=     |         |                                          |       |       |       |       |       |       |      |   |  |

| vire                                                      | z behavioral   | z_benavioral<br>z dataflow= |         |                                          |       |       |       |       |       |       |      |   |  |

| vire                                                      | z_dataflow     | 2_dataitow-                 |         |                                          |       |       |       |       |       |       |      |   |  |

| ilter:                                                    |                | 1                           |         |                                          |       |       |       |       |       |       |      |   |  |

- Here you can GTKWave viewing the dumbed variables from the self-checking testbench

- The idea is basically to mimic an oscilloscope

- It's fairly intuitive and easy to use, without any real "gotchas" in my opinion, so I won't spend too long on it

Simulation/Debugging Synthesis

• Open source "digital synthesis flow"

- Most problematic tool

- May just be my lack of experience

- Combines other tools:

- yosys: Verilog synthesis/optimization

- graywolf: Placement tool

- qrouter: Routing tool

Qflow [7]

```

Open Source Digital Logic Design

```

- Now onto synthesis which is the process of turning your module into a real circuit

- The best Open Source synthesis tool I've found so far is Qflow

- That being said, I still run into a lot of errors with this tool, so I'd definitely say it's the biggest problem area

- However, it is also the tool I have the least experience with, since I normally have to use closed-source versions of tools for my classes

- From my understanding, Qflow is basically a wrapper around a series of other open source tools, like yosys, graywolf, grouter and more in an attempt to automate the process

Simulation/Debugging Synthesis

### Installation issues

**Note:** These issues were present as of August 31, 2021; some of these issues will likely be fixed upstream in the coming months

- Graywolf: Compilation issue due to globals<sup>1</sup>

- **netgen**: Compilation issue due to security flag<sup>2</sup>

- Qflow: Bad ABC symlink<sup>3</sup>

https://github.com/rubund/graywolf/issues/43

<sup>2</sup> https://aur.archlinux.org/packages/netgen-lvs-git/#comment-822826

<sup>3</sup> https://stackoverflow.com/questions/36593907/

- While installing Qflow and its associated packages, I ran into a few errors that you should be aware of if you want to try this yourself

- Hopefully, these issues will be fixed in the coming months; I found two of them and their fixes myself, and plan on reporting them once I have some more information

- The first issue is with Graywolf; some global values are defined twice; the temporary fix involves just updating the makefile to resolve the issue

- The next issue I ran into was with installing netgen; it was also a compilation issue, where the temporary fix was also just updating the makefile

- The final issue I ran into during installation was with Qflow, which apparently assumes the location of ABC, so it creates a symlink to the wrong location. This can be fixed simply by figuring out where ABC actually installed and updating the symlink.

Simulation/Debugging Synthesis

# Results

Results from following tutorial<sup>1</sup>:

If your design is too simple, you'll run into errors<sup>2</sup>

http://opencircuitdesign.com/qflow/tutorial.html

http://opencircuitdesign.com/pipermail/eda-dev/2021-August/thread.html

Davis Claiborne

Open Source Digital Logic Design

```

Open Source Digital Logic Design

```

- Once you've got Qflow installed, you can follow the tutorial to see what the chip would look like

- You should not that it's not just a fire and forget process, as some parameters will need to be tweaked depending on what you're doing

- For instance, while trying to synthesize the simple and module we've been using through this presentation, I ran into errors

- This basically happened because the design was so small that it couldn't place power or ground properly. So just keep in mind that you will need to tweak some things to get it to work.

Simulation/Debugging Synthesis

## More software/resources

In no particular order:

- **OpenROAD**: Attempt at fully automated EDA [9]

- Verilator: Compiles Verilog to C++; considered using it, but tests need to also be done in C++ [8]

- Electric: Integrated-Circuit design tool [5]

- Circuit\_macros: Tool for producing typeset schematics [1]

- **Digital**: Java-based tool for designing and simulating digital logic [3]

- DigitalJS: Online interactive Verilog tool [4]

- · Of course, the software I've shown off here isn't the only software that exists

- There are a bunch of open source tools that I didn't show off, or just don't know about or use

- The first one, OpenROAD, from what I can tell is an attempt to make a fully automated HDL to hardware

pipeline; I have not tried it out yet, but intend to give it a try soon

- Verilator is a Verilog simulator that simulates by converting the Verilog to C++; I considered using this, and it does look interesting, but to use it you need to write your tests in C++, since it only supports converting the synthesizable subset of Verilog; I may check it out in the future, but for now CVC works well enough

- Electric is an entire suite for designing ICs; I hadn't heard about it until recently, but it looks pretty neat; from what I can tell, it doesn't support synthesizing from Verilog, but it looks like a useful tool for other hardware design needs

- Circuit\_macros is the tool I used to produce all the logic gates for this presentation; it's basically like graphviz for circuits, although not quite as automated as I'd like it to be

- Digital and DigitalJS are both interactive tools for designing digital logic; Digital includes logic optimization tools, while DigitalJS runs in-browser and can read Verilog, which can be useful for debugging modules

#### References I

#### Software

- Circuit\_macros—Typesetting tool for producing schematics https://ece.uwaterloo.ca/~aplevich/Circuit\_macros/

- [2] CVC—Verilog simulator that compiles to x86 for speed http://www.tachyon-da.com/what-is-cvc/

- [3] Digital—Tool for digital logic design/simulation https://github.com/hneemann/Digital

- [4] DigitalJS—Online tool for viewing Verilog http://digitaljs.tilk.eu/

- [5] Electric—Integrated-Circuit Design system https://www.staticfreesoft.com/index.html

- [6] gEDA Projects—Collection of GPLd EDA tools, including Icarus Verilog and GTKWave http://www.geda-project.org/

- [7] Open Circuit Design—Collection of open-source EDA tools, including Qflow http://opencircuitdesign.com/

- [8] Verilator—Verilog transpiler to C++ https://www.veripool.org/verilator/

- [9] OpenROAD—Goal is to make fully automated HDL to hardware pipeline https://theopenroadproject.org/

#### Websites

[10] Karnaugh-Veitch Map—Performs groupings for 4 to 8 variable k-maps https://www.mathematik.uni-marburg.de/~thormae/lectures/til/code/karnaughmap/

#### Images

- [11] Claude Shannon https://en.wikipedia.org/wiki/Claude\_Shannon#/media/File:ClaudeShannon\_MF03807.jpg

- [12] De Morgan's law https://upload.wikimedia.org/wikipedia/commons/0/06/Demorganlaws.svg

- [13] K-map on a torus https://upload.wikimedia.org/wikipedia/commons/3/33/Karnaugh\_map\_torus.svg